Untangling the Clock Tree of an STM32L4S5xx Microcontroller !

What is the Clock Tree?

The clock tree is a hierarchical structure within a microcontroller that distributes clock signals to various parts of the chip. It consists of Clock Sources, Distribution networks, Clock-Gating elements, and Multiplexers to choose specific clock sources. The clock tree ensures that all parts of the chip receive synchronized clock signals and operate in sync with each other, preventing timing issues. Clock gating elements in the clock tree can selectively disable clock signals to unused or idle parts of the chip, reducing power consumption. Read the Wikipedia page on Clock Signal to learn more about the Clock sources and Clock Distribution Network.

Clock Sources for the Microcontroller

The clock sources available in the STM32L4S5 are

- 16 MHz High-Speed Internal RC Oscillator clock (HSI16)

- Multispeed Internal RC Oscillator clock (MSI)

- 4 MHz - 48 MHz High-Speed External Oscillator Clock (HSE-OSC)

- Internal Phase Locked Loop (PLLCLK)

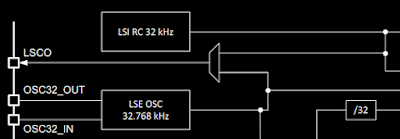

- 32 kHz Low-Speed Internal RC Oscillator clock (LSI32)

- 32.768 kHz Low-Speed External Crystal (LSE-OSC)

- 48 MHz High-Speed Internal RC Oscillator Clock (HSI48)

Of the 7 sources listed above, HSI16, MSI, HSI48, and LSI32 are purely internal sources. The HSE-OSC and LSE-OSC clock sources are external to the microcontroller. But, the PLL blocks ( there is more than one ) are internal clock sources but they get their clock from the MSI, HSI16, or the HSE-OSC.

In the following sections, we will refer to each clock source by the names given in the parentheses.

Internal Sources v/s External Sources

The Internal Clock sources listed above relies on an internal oscillator circuit. Internal clock sources are convenient because they eliminate the need for an external clock component. But, they may not always be as accurate or stable as external clock sources. External Clock sources uses a crystal oscillator or an external clock generator to provide the clock signal. External clock sources are preferred in applications where precise timing is crucial. In some applications, the microcontroller may require synchronization with other external devices, which is easier to achieve with an external clock source. For example, multiple microcontrollers in a single system might choose to use a single external clock source.

Phase Locked Loop Blocks

The Phase Locked Loop (PLL) can be used to multiply the frequency of the clock signal provided to it as input. The STM32L4S5 has 3 PLL Blocks, they are:

- Main PLL Block

.png) This block takes its input from either the MSI, HSI16, or the HSE-OSC. It can be configured by the PLLSRC bits in the RCC_PLLCFGR register. As you can see, it gives three outputs, a clock to the Serial Audio Interface 3 Peripheral, a dedicated 48 MHz clock and the PLLCLK to the System Clock. Among these, the PLLCLK is used to drive the System Clock to 120 MHz if needed.

This block takes its input from either the MSI, HSI16, or the HSE-OSC. It can be configured by the PLLSRC bits in the RCC_PLLCFGR register. As you can see, it gives three outputs, a clock to the Serial Audio Interface 3 Peripheral, a dedicated 48 MHz clock and the PLLCLK to the System Clock. Among these, the PLLCLK is used to drive the System Clock to 120 MHz if needed. - PLLSAI1 Block

.png) This block has the same input as that of the Main PLL Block configured by the PLLSRC bits in the RCC_PLLCFGR register. Same as before, this block also gives out three outputs, a Clock to the Serial Audio Interface 1 peripheral, ADC1 Peripheral, and a dedicated 48MHz Clock to the OCTOSPI peripheral and the USB-OTG & RNG peripherals.

This block has the same input as that of the Main PLL Block configured by the PLLSRC bits in the RCC_PLLCFGR register. Same as before, this block also gives out three outputs, a Clock to the Serial Audio Interface 1 peripheral, ADC1 Peripheral, and a dedicated 48MHz Clock to the OCTOSPI peripheral and the USB-OTG & RNG peripherals. - PLLSAI2 Block

System Clock

System Clock (SYSCLK ) is the main clock signal that drives the operation of the microcontroller's core and peripherals. The SYSCLK frequency determines the speed at which the microcontroller executes instructions and operates its peripherals. The SYSCLK is often divided down to generate other clock signals used by different parts of the microcontroller, such as the CPU, Timers, UART etcetera.

When the microcontroller Powers Up (including after reset), the MSI at 4 MHz is used as the System Clock. The user can choose to switch between HSE-OSC, MSI, HSI16 and PLLCLK as the system clock by configuring the RCC_CFGR register. Note that, shooting up the clock from the reset value of 4 MHz to 120 MHz should be done in steps and not suddenly. Specific instructions can be found in the Reference Manual (RM0432).

Microcontroller Clock Output (MCO)

GPIO Pins can be configured into Alternate Function mode to provide clock output from any of the seven clock sources available and in addition to that, the System Clock. A Multiplexer in the clock tree determines which one is selected as the MCO. It can be configured via software using the MCOSEL bits in the RCC_CFGR register. Note that, the MCO can also be scaled down if required.

When Low-Speed Clock signals are required, the LSCO feature can be used that uses either the LSE-OSC or the LSI to provide clock output. This clock output, however, cannot be scaled down.

AHB and APB Domain Clocks

The Advanced High-Performance Bus (AHB) and Advanced Peripheral Bus (APB) are connected to the Cortex-M4 CPU and the Peripherals, except a few special ones. These buses use the clock provided by the System Clock for it's operations. The AHB Prescaler scales down the clock from SYSCLK before passing it to the AHB Bus, APB1 Bus, and APB2 Bus.

The HCLK is passed along to the APB1 Prescaler and APB2 Prescaler in addition to that depicted in the above image. The APB1 Prescaler can scale down the clock if the user configures the PPRE1 bits in the RCC_CFGR register.

From here, PCLK1 is passed to the Timers, Low-Power Timers, USARTs, I2Cs, and the rest of the APB1 Peripherals. The HCLK passed along to the APB2 Prescaler can be scaled down by configuring the PPRE2 bits in the RCC_CFGR register.

Special Clock Requirements

This section will talk about the Peripherals that use clock sources other than the System Clock. Some of these peripherals have the option to choose System Clock in addition to the other sources.

- Independent Watchdog Timer (IWDG)

Sources the clock from the 32kHz LSI RC Oscillator. - Real-Time Clock (RTC)

Chooses between LSI, LSE-OSC, and HSE-OSC as the clock source. - Secure Digital input/output and MultiMediaCards Interface (SDMMC)

Chooses between HSI48, MSI, PLLSAI3CLK, PLL48M1CLK, or PLL48M2CLK. - OctoSPI Interface (OCTOSPI)

Choose between SYSCLK, MSI, or PLL48M2CLK. - Clock Recovery System (CRS)

Sources the clock from the HSI48 RC Oscillator. - Universal Serial Bus On-The-Go (USB-OTG) and Random Number Generator (RNG)

Chooses between HSI48, MSI, PLL48M1CLK, or PLL48M2CLK. - Analog to Digital Converter (ADC)

Choose between SYSCLK and PLLADC1CLK. - Display Serial Interface Host (DSI)

The DSI Rx Escape Mode Clock is sourced from the HSE-OSC with an upper limit of 20 MHz. The DSI Byte Lane Clock is sourced from either the HSE-OSC or PLLDSICLK. - Digital filter for sigma-delta modulators (DFSDM)

Chooses between MSI, HSI16, PLLSAI1CLK, PLLSAI2CLK, PLLSAI3CLK or the SAI1_EXTCLK. - TFT-LCD Display Controller (LTDC)

Uses the PLLCDCCLK from the PLLSAI2 Block. - Serial Audio Interface (SAI)

SAI1 can choose between HSI16, PLLSAI1CLK, PLLSAI2CLK, PLLSAI3CLK or the SAI1_EXTCLK. SAI2 can choose between HSI16, PLLSAI1CLK, PLLSAI2CLK, PLLSAI3CLK or the SAI2_EXTCLK.

Check out the Datasheet and Reference Manual for your specific microcontroller to understand how your Clock is distributed and sourced.

.png)

.png)

.png)

.png)

.png)

.png)